Zynq软件开发基础 从架构认知到设计实践

Zynq系列是赛灵思(Xilinx,现AMD)推出的集成了ARM处理器与FPGA可编程逻辑的片上系统(SoC)。其软件开发需要跨越传统嵌入式软件与硬件逻辑设计两个领域,理解其独特的架构和开发流程是进行高效软件设计与开发的基础。

一、 Zynq架构的核心认知

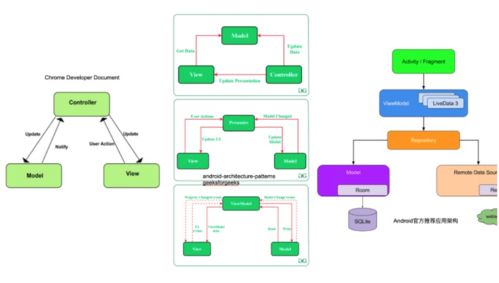

Zynq的核心在于其双核ARM Cortex-A9处理系统(PS)与FPGA可编程逻辑(PL)的紧密耦合。PS是一个完整的、独立的处理器系统,可以像传统微处理器一样运行操作系统(如Linux)和应用程序。PL则提供了硬件可编程的并行加速能力。两者通过高速AXI互连总线进行通信,数据带宽高、延迟低,这是Zynq实现软硬件协同加速的关键。

二、 软件开发流程与工具链

Zynq的软件开发通常遵循一个层次化的流程:

- 硬件平台定义:首先在Vivado设计套件中,使用IP集成器配置PS端(如时钟、DDR、外设)并添加PL端的自定义IP核,生成完整的硬件描述文件(.xsa或旧的.hdf文件)。这是后续软件开发的硬件基础。

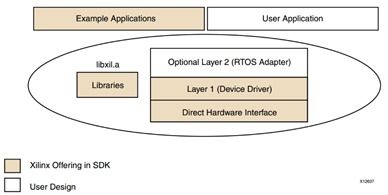

- 板级支持包(BSP)与操作系统:在Xilinx Vitis统一软件平台(或旧的SDK)中,基于硬件描述文件创建或导入一个软件平台项目。这为PS生成了底层的板级支持包,包含启动代码(FSBL)、外设驱动以及可选的操作系统(如裸机、FreeRTOS或Linux)。

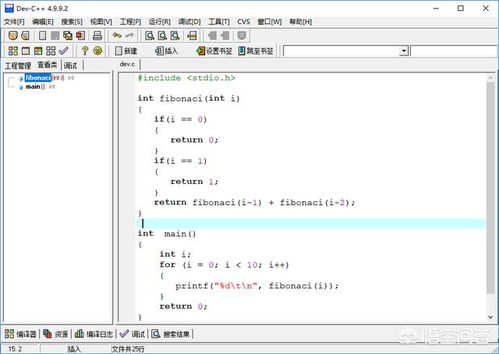

- 应用程序开发:在Vitis中创建应用工程,针对目标平台(裸机或操作系统)编写C/C++应用程序。对于涉及PL加速的功能,应用程序需要通过驱动或直接内存访问(DMA)与PL端的IP核进行数据交互。

三、 软件设计的关键概念与实践

- 地址空间与内存映射:理解Zynq的地址映射至关重要。PS和PL共享同一物理地址空间(主要通过DDR内存)。应用程序访问PL中的自定义IP寄存器,本质上是通过内存映射I/O(MMIO)访问特定的物理地址。Vivado中配置的IP地址空间必须在软件中正确定义才能正确驱动。

- 启动流程:Zynq的启动是一个多阶段过程。通常从PS端的BootROM开始,然后加载第一阶段引导程序(FSBL),FSBL负责配置PS、初始化DDR并加载PL的比特流文件(如果需要),最后加载并跳转到第二阶段的应用程序(裸机程序)或操作系统的引导程序(如U-Boot)。掌握此流程有助于调试启动问题。

- PS与PL的通信机制:

- 轮询与中断:PS可以通过轮询PL IP的状态寄存器,或配置PL产生中断来通知PS事件,后者效率更高。

- DMA数据传输:对于PL与PS DDR之间的大量数据搬移,使用AXI DMA IP核是标准做法,可以极大解放CPU,实现高速数据流。

- 共享内存:PS和PL通过片上存储器(OCM)或DDR中的共享内存区域进行数据交换,这是一种高效的数据共享方式。

- 性能优化考虑:在软件设计时,需考虑缓存一致性(尤其是PS与PL共享DDR数据时)、数据对齐、以及利用PL进行算法硬件加速来分担CPU负载。分析应用的性能瓶颈,决定哪些部分适合用PL并行实现,是Zynq软硬件协同设计的精髓。

四、 调试与测试

Zynq提供了强大的调试能力。通过JTAG接口,可以同时调试PS端的ARM核(使用Vitis调试器)和PL端的逻辑(使用Vivado逻辑分析仪ILA)。对于运行Linux的系统,还可以通过串口、网络等接口进行应用层调试。

###

掌握Zynq软件开发,需要建立起“软硬一体”的思维模式。从理解其异构架构出发,熟悉Vivado/Vitis工具链的标准流程,并深刻把握PS与PL协同工作的通信机制与性能优化方法。这为在嵌入式系统中实现高性能、低功耗、高灵活性的解决方案奠定了坚实的基础。

如若转载,请注明出处:http://www.ncf88888.com/product/48.html

更新时间:2025-12-20 08:06:31